様々な物のパッキングに関する研究

メンバー: 藤吉邦洋

分野: 電気電子工学、情報学基礎

所属: 工学研究院

キーワード: パッキング、面積最小、長方形、多角形、直方体、型紙

ウェブサイト:

研究概要

与えられた複数の物を、限られた領域、もしくは出来るだけ小さい領域にパッキングするという問題は、様々な場面、例えば、カバンや車に荷物を詰め込むとき、板などの素材から指定された形状の部品を切り出さねばならないときなどに出くわします。それだけでなく、この問題に様々な条件を加えた問題は集積回路設計などにおいて、高性能な集積回路を低コストで生産するため、効率良く解けることが望まれています。

このパッキング問題に対して密な解を求める方法は幾つかありますが、その中でも有力なものの一つが、素材同士が重ならないことを保証して素材の相対位置関係を与えるというトポロジカルな表現を用いて、密なパッキングを探索する方法です。我々は、この方法に基づいて効率良く密な解を見つけ出す方法についての研究を行っていますが、そのためには、良い表現方法を作り出すことが最も重要です。そして、様々なパッキング問題の中で、我々は既に、

(1) 与えられた複数の長方形を長方形内に詰めるパッキング問題、

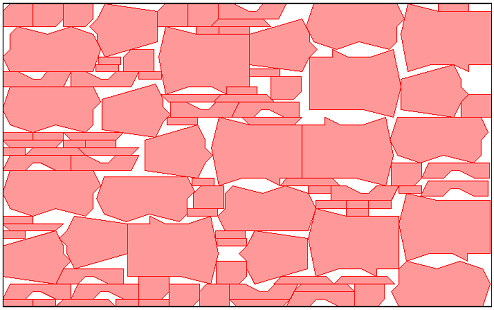

(2) 内角が全て90度もしくは270度な多角形であるレクトリニア多角形が複数与えられ、これらを長方形内に詰めるパッキング問題、

(3) マーキングと呼ばれている、複雑な形状である洋服の型紙を複数与えられ、これらを布地にパッキングする問題、

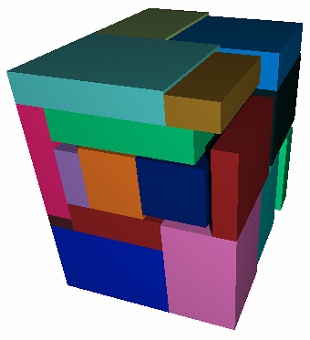

(4) 与えられた複数の直方体を直方体内に詰める3次元のパッキング問題、

について研究を行っており、成果を得ております。

主要論文・参考事項

[1] H. Murata, K. Fujiyoshi, S. Nakatake, and Y. Kajitani: "VLSI Module Placement Based on Rectangle-Packing by the Sequence-Pair", IEEE Trans. Computer-Aided Design, Vol.15, No.12, pp.1518-1524, 1996.

[2] S. Nakatake, K. Fujiyoshi, H. Murata, and Y. Kajitani: "Module Packing Based on the BSG-Structure and IC Layout Applications", IEEE Trans. Computer-Aided Design, Vol.17, No.6, pp.519-530, 1998.

[3] K. Fujiyoshi, and H. Murata: "Arbitrary Convex and Concave Rectilinear Block Packing Using Sequence-Pair", IEEE Trans. Computer-Aided Design, Vol.19, No.2, pp.224-233, 2000.

[4] S. Koda, C. Kodama, and K. Fujiyoshi: "Linear Programming-Based Cell Placement with Symmetry Constraints for Analog IC Layout", IEEE Trans. Computer-Aided Design, Vol.26, No.4, pp.659-668, 2007.

[5] K. Fujiyoshi, H. Kawai, and K. Ishihara: "A Tree Based Novel Representation for 3D-Block Packing", IEEE Trans. Computer-Aided Design, Vol.28, No.5, pp.759-764, 2009.

[6] 原田 昌之, 大島 津佳, 藤吉 邦洋: "Simulated Annealing法に基づいた自動マーキングシステムの一手法", 電子情報通信学会 技術研究報告, CAS2013-34, pp.189-193, 2013.

お問い合わせ先

東京農工大学・先端産学連携研究推進センター

urac[at]ml.tuat.ac.jp([at]を@に変換してください)

Research for various kinds of packings

Research members: Dr. Kunihiro Fujiyoshi

Research fields: Electrical and electronic engineering, Principles of Informatics (1)

Departments: Institute of Engineering

Keywords: packing, minimum area, rectangle, polygon, rectangular box, paper pattern

Web site:

Summary

We sometimes have to pack some given objects into a region of given size, or into a smallest region, when some given boxes should be packed into a suitcase or a car, or when some parts of given shapes should be obtained from a plate by cutting. Since this problem, called "packing problem", is a basic problem of layout design of LSI, it is also very important to solve it efficiently in industry.

To solve the packing problem, several methods are proposed and studied. One of the famous methods is to represent packings by topological representations and to search for representations corresponding to good packings by stochastic search algorithm. Our researches are based on the topological representation, and our research targets include:

(1) rectangle packing,

(2) rectilinear polygon packing (interior angles of the polygon are 90 or 270 degrees only),

(3) "marking", which is to pack paper patterns of clothes,

(4) rectangular box packing (3-dimensional packing).

Reference articles and patents

[1] H. Murata, K. Fujiyoshi, S. Nakatake, and Y. Kajitani: "VLSI Module Placement Based on Rectangle-Packing by the Sequence-Pair", IEEE Trans. Computer-Aided Design, Vol.15, No.12, pp.1518-1524, 1996.

[2] S. Nakatake, K. Fujiyoshi, H. Murata, and Y. Kajitani: "Module Packing Based on the BSG-Structure and IC Layout Applications", IEEE Trans. Computer-Aided Design, Vol.17, No.6, pp.519-530, 1998.

[3] K. Fujiyoshi, and H. Murata: "Arbitrary Convex and Concave Rectilinear Block Packing Using Sequence-Pair", IEEE Trans. Computer-Aided Design, Vol.19, No.2, pp.224-233, 2000.

[4] S. Koda, C. Kodama, and K. Fujiyoshi: "Linear Programming-Based Cell Placement with Symmetry Constraints for Analog IC Layout", IEEE Trans. Computer-Aided Design, Vol.26, No.4, pp.659-668, 2007.

[5] K. Fujiyoshi, H. Kawai, and K. Ishihara: "A Tree Based Novel Representation for 3D-Block Packing", IEEE Trans. Computer-Aided Design, Vol.28, No.5, pp.759-764, 2009.

[6] 原田 昌之, 大島 津佳, 藤吉 邦洋: "Simulated Annealing法に基づいた自動マーキングシステムの一手法", 電子情報通信学会 技術研究報告, CAS2013-34, pp.189-193, 2013.

Contact

University Research Administration Center(URAC),

Tokyo University of Agriculture andTechnology

urac[at]ml.tuat.ac.jp

(Please replace [at] with @.)